Is The Register The Size Of An Address

Assembly - Registers

Processor operations generally involve processing data. This data can be stored in memory and accessed from thereon. However, reading information from and storing information into memory slows downwardly the processor, as it involves complicated processes of sending the data asking across the control omnibus and into the memory storage unit and getting the data through the same aqueduct.

To speed up the processor operations, the processor includes some internal memory storage locations, chosen registers.

The registers store information elements for processing without having to access the retention. A express number of registers are built into the processor chip.

Processor Registers

There are ten 32-bit and six 16-bit processor registers in IA-32 architecture. The registers are grouped into three categories −

- General registers,

- Control registers, and

- Segment registers.

The full general registers are farther divided into the following groups −

- Data registers,

- Pointer registers, and

- Index registers.

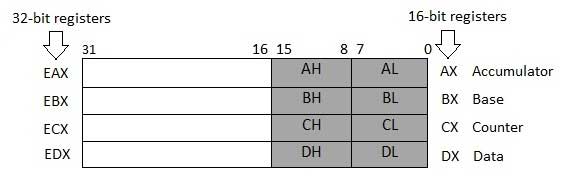

Information Registers

Four 32-bit information registers are used for arithmetic, logical, and other operations. These 32-fleck registers can be used in three means −

-

As complete 32-bit data registers: EAX, EBX, ECX, EDX.

-

Lower halves of the 32-bit registers can be used as 4 16-bit data registers: AX, BX, CX and DX.

-

Lower and college halves of the to a higher place-mentioned 4 16-flake registers can exist used equally eight 8-bit data registers: AH, AL, BH, BL, CH, CL, DH, and DL.

Some of these data registers take specific employ in arithmetical operations.

AX is the primary accumulator; it is used in input/output and well-nigh arithmetic instructions. For example, in multiplication functioning, 1 operand is stored in EAX or AX or AL register according to the size of the operand.

BX is known every bit the base annals, equally it could be used in indexed addressing.

CX is known as the count register, equally the ECX, CX registers store the loop count in iterative operations.

DX is known equally the data register. It is also used in input/output operations. It is besides used with AX register along with DX for multiply and divide operations involving large values.

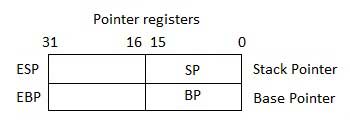

Arrow Registers

The arrow registers are 32-bit EIP, ESP, and EBP registers and respective xvi-bit correct portions IP, SP, and BP. There are three categories of pointer registers −

-

Instruction Pointer (IP) − The 16-bit IP register stores the offset address of the next education to be executed. IP in association with the CS annals (as CS:IP) gives the complete address of the electric current education in the code segment.

-

Stack Pointer (SP) − The 16-flake SP register provides the offset value within the programme stack. SP in clan with the SS register (SS:SP) refers to exist current position of data or address inside the plan stack.

-

Base of operations Pointer (BP) − The 16-flake BP register mainly helps in referencing the parameter variables passed to a subroutine. The address in SS annals is combined with the get-go in BP to get the location of the parameter. BP tin also be combined with DI and SI as base register for special addressing.

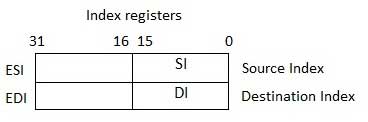

Alphabetize Registers

The 32-bit index registers, ESI and EDI, and their sixteen-bit rightmost portions. SI and DI, are used for indexed addressing and sometimes used in addition and subtraction. There are two sets of index pointers −

-

Source Index (SI) − It is used every bit source index for string operations.

-

Destination Index (DI) − It is used as destination index for string operations.

Control Registers

The 32-chip instruction pointer register and the 32-bit flags register combined are considered as the command registers.

Many instructions involve comparisons and mathematical calculations and alter the status of the flags and another provisional instructions exam the value of these status flags to take the control menstruation to other location.

The common flag bits are:

-

Overflow Flag (OF) − It indicates the overflow of a high-social club bit (leftmost bit) of data later a signed arithmetic operation.

-

Direction Flag (DF) − It determines left or correct direction for moving or comparing string information. When the DF value is 0, the string operation takes left-to-right management and when the value is set to ane, the string functioning takes correct-to-left direction.

-

Interrupt Flag (IF) − Information technology determines whether the external interrupts like keyboard entry, etc., are to exist ignored or processed. It disables the external interrupt when the value is 0 and enables interrupts when set to one.

-

Trap Flag (TF) − It allows setting the operation of the processor in single-step mode. The DEBUG program we used sets the trap flag, then we could step through the execution 1 education at a fourth dimension.

-

Sign Flag (SF) − It shows the sign of the result of an arithmetic performance. This flag is set according to the sign of a data particular post-obit the arithmetic performance. The sign is indicated by the high-order of leftmost bit. A positive result clears the value of SF to 0 and negative effect sets information technology to one.

-

Zero Flag (ZF) − It indicates the effect of an arithmetic or comparison functioning. A nonzero result clears the aught flag to 0, and a goose egg result sets information technology to 1.

-

Auxiliary Deport Flag (AF) − It contains the deport from bit 3 to chip 4 following an arithmetic performance; used for specialized arithmetics. The AF is set when a 1-byte arithmetics functioning causes a carry from bit 3 into flake 4.

-

Parity Flag (PF) − It indicates the full number of 1-$.25 in the result obtained from an arithmetic operation. An fifty-fifty number of 1-bits clears the parity flag to 0 and an odd number of i-bits sets the parity flag to 1.

-

Carry Flag (CF) − It contains the carry of 0 or 1 from a high-gild scrap (leftmost) subsequently an arithmetics performance. It also stores the contents of final scrap of a shift or rotate operation.

The following table indicates the position of flag bits in the 16-bit Flags register:

| Flag: | O | D | I | T | S | Z | A | P | C | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Flake no: | 15 | 14 | 13 | 12 | 11 | ten | 9 | 8 | 7 | half-dozen | 5 | 4 | three | 2 | 1 | 0 |

Segment Registers

Segments are specific areas defined in a program for containing data, code and stack. There are 3 main segments −

-

Lawmaking Segment − It contains all the instructions to be executed. A 16-bit Lawmaking Segment register or CS register stores the starting accost of the code segment.

-

Data Segment − It contains data, constants and work areas. A 16-chip Data Segment register or DS annals stores the starting address of the data segment.

-

Stack Segment − Information technology contains data and return addresses of procedures or subroutines. It is implemented as a 'stack' information structure. The Stack Segment register or SS annals stores the starting address of the stack.

Apart from the DS, CS and SS registers, there are other extra segment registers - ES (extra segment), FS and GS, which provide additional segments for storing data.

In assembly programming, a plan needs to admission the retention locations. All memory locations within a segment are relative to the starting accost of the segment. A segment begins in an address evenly divisible by 16 or hexadecimal 10. So, the rightmost hex digit in all such memory addresses is 0, which is not mostly stored in the segment registers.

The segment registers stores the starting addresses of a segment. To get the exact location of data or pedagogy inside a segment, an showtime value (or deportation) is required. To reference any memory location in a segment, the processor combines the segment address in the segment annals with the offset value of the location.

Instance

Look at the post-obit uncomplicated program to understand the use of registers in associates programming. This plan displays ix stars on the screen along with a simple message −

section .text global _start ;must exist alleged for linker (gcc) _start: ;tell linker entry bespeak mov edx,len ;message length mov ecx,msg ;bulletin to write mov ebx,1 ;file descriptor (stdout) mov eax,4 ;system call number (sys_write) int 0x80 ;call kernel mov edx,nine ;message length mov ecx,s2 ;bulletin to write mov ebx,i ;file descriptor (stdout) mov eax,4 ;arrangement telephone call number (sys_write) int 0x80 ;call kernel mov eax,1 ;organization telephone call number (sys_exit) int 0x80 ;call kernel section .data msg db 'Displaying 9 stars',0xa ;a message len equ $ - msg ;length of message s2 times 9 db '*'

When the above lawmaking is compiled and executed, it produces the following effect −

Displaying 9 stars *********

Is The Register The Size Of An Address,

Source: https://www.tutorialspoint.com/assembly_programming/assembly_registers.htm

Posted by: lukenrion1963.blogspot.com

0 Response to "Is The Register The Size Of An Address"

Post a Comment